5月11日消息 据国家信息光电子创新中心公众号消息,近日,国家信息光电子创新中心(NOEIC)和鹏城实验室的光电融合联合团队完成了2Tb/s硅光互连芯粒(chiplet)的研制和功能验证,在国内首次验证了3D硅基光电芯粒架构,实现了单片最高达8×256Gb/s的单向互连带宽。

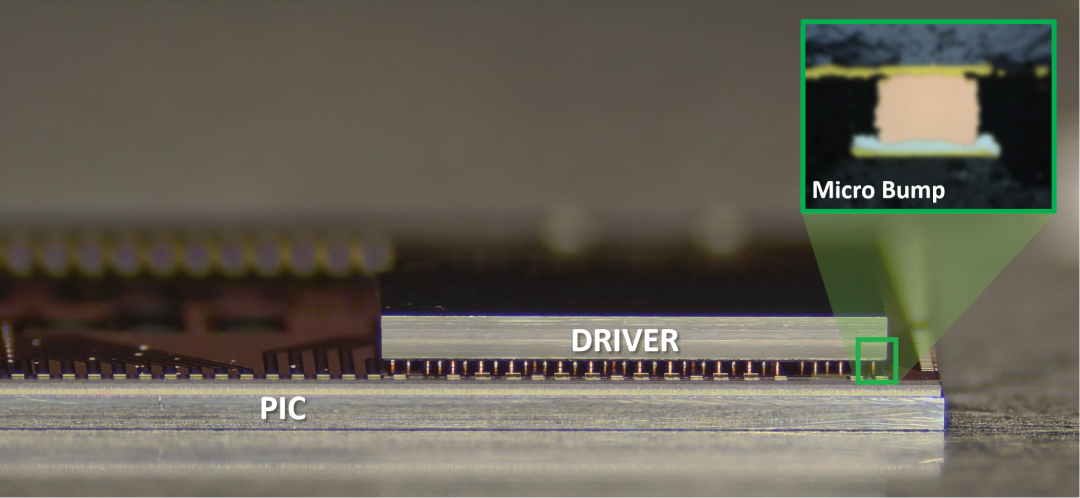

据了解,团队在2021年1.6T硅光互连芯片的基础上,进一步突破了光电协同设计仿真方法,研制出硅光配套的单路超200G driver和TIA芯片,并攻克了硅基光电三维堆叠封装工艺技术,形成了一整套基于硅光芯片的3D芯粒集成方案。

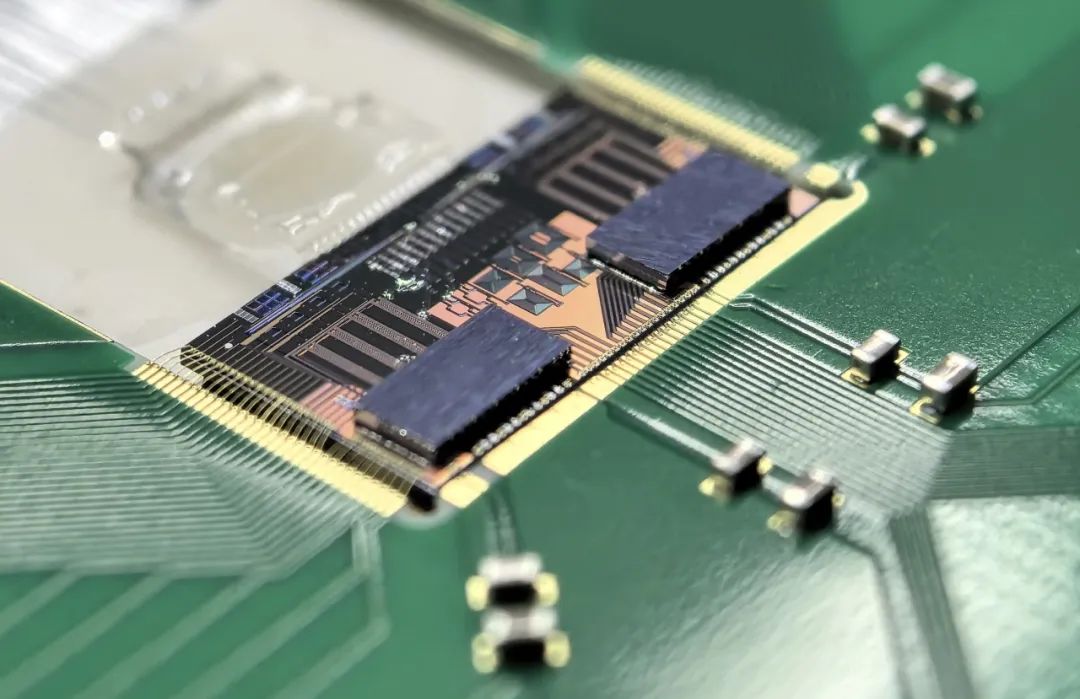

2Tb/s 硅基3D集成光发射芯粒

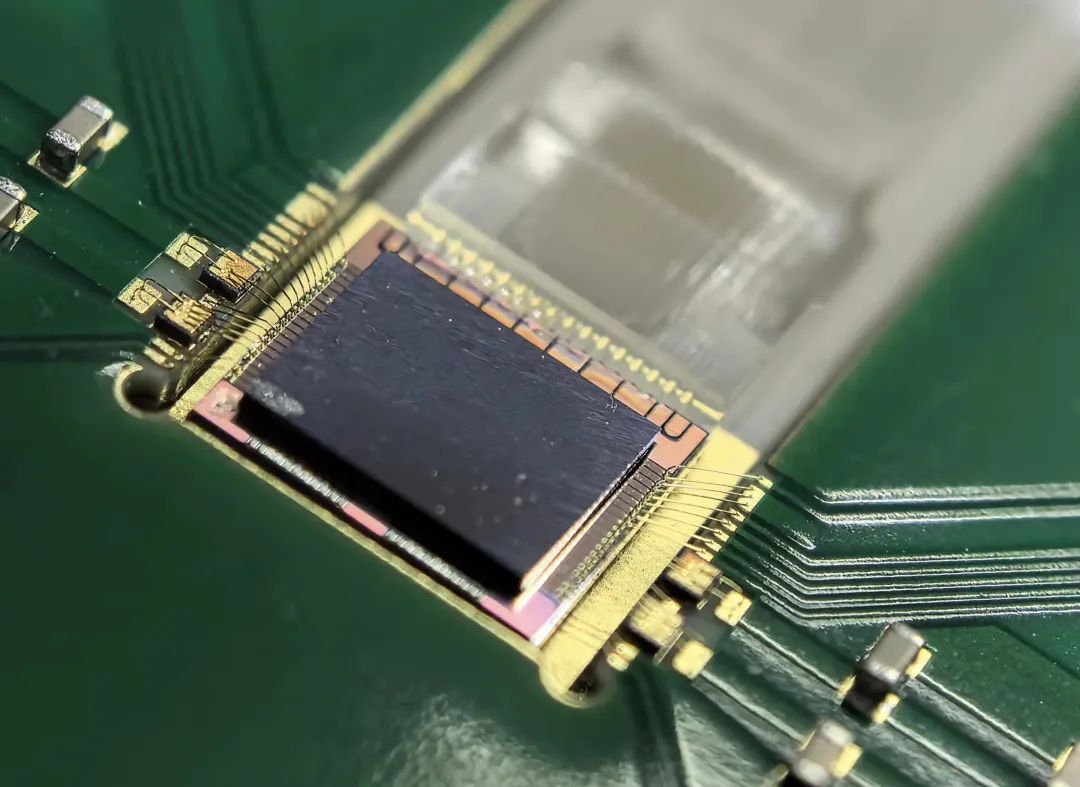

2Tb/s 硅基3D集成光接收芯粒

硅光互连芯粒的侧向显微镜结构

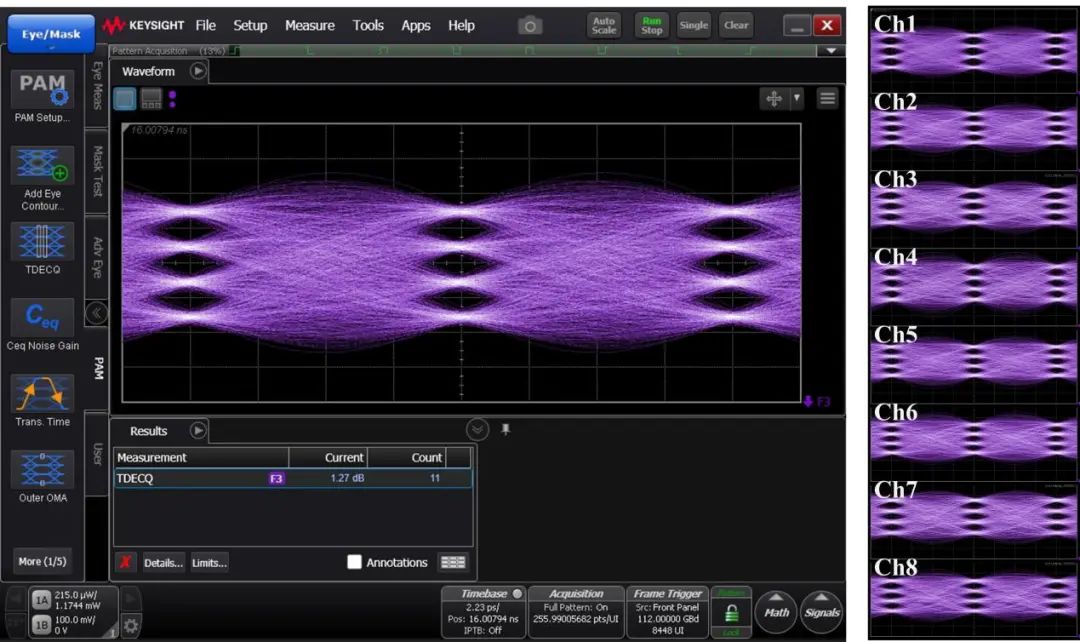

该方案充分利用了硅光与CMOS封装工艺兼容的特点,相比于传统wirebond方案,3D芯粒能解决电芯片与光芯片间高密度、高带宽电互连的困难,显著降低射频信号在光-电芯片互连过程中的严重衰减。经系统传输测试,8个通道在下一代光模块标准的224Gb/s PAM4光信号速率下,TDECQ均在2dB以内。通过进一步链路均衡,最高可支持速率达8×256Gb/s,单片单向互连带宽高达2Tb/s。

8×224Gb/s硅基光发射芯粒输出眼图

据透露,该工作充分展现了3D集成硅光芯粒的优越互连性能,以及联合团队的领先自主研发水平。成果将广泛应用于下一代算力系统和数据中心所需的CPO、NPO、LPO、LRO等各类光模块产品中,为国内信息光电子技术的率先突围探索出可行路径。

硅光已经是目前全球光模块市场的主流技术之一。LightCounting此前预计,使用基于SiP的光模块市场份额将从2022年的24%增加到2028年的44%。

- 千家早报|海尔新能源获超7亿元A轮融资;中国成为全球人工智能专利最大拥有国,占比60%——2025年04月27日

- 光模块“四剑客”的2024年:AI仍是主战场,国内节奏明显加快

- “领跑行动”启动!中国联通加码布局马拉松赛事

- 存储双雄!长江存储估值1600亿,长鑫存储估值1400亿

- 中国移动、中国联通三大算力项目获备案:总投资超141亿元

- 陈山枝博士两部专著入选中国知网“高被引图书TOP 1%(2019-2023)”榜单!

- 解析百度“高说服力数字人”:AI技术如何说服用户“买买买”?

- 内蒙古:2025年积极布局低空经济 做大低空制造业

- Gartner:2024年全球半导体收入增长 21% 英伟达首次跃居首位

- 识风口、找航道、植沃土:超聚变领航算力产业破浪智能体时代

免责声明:本网站内容主要来自原创、合作伙伴供稿和第三方自媒体作者投稿,凡在本网站出现的信息,均仅供参考。本网站将尽力确保所提供信息的准确性及可靠性,但不保证有关资料的准确性及可靠性,读者在使用前请进一步核实,并对任何自主决定的行为负责。本网站对有关资料所引致的错误、不确或遗漏,概不负任何法律责任。任何单位或个人认为本网站中的网页或链接内容可能涉嫌侵犯其知识产权或存在不实内容时,应及时向本网站提出书面权利通知或不实情况说明,并提供身份证明、权属证明及详细侵权或不实情况证明。本网站在收到上述法律文件后,将会依法尽快联系相关文章源头核实,沟通删除相关内容或断开相关链接。