不久前在旧金山举办的ISSCC国际固态电路会议上,东芝公开讨论了新一代96层堆叠3D QLC闪存的细节,并介绍了未来128层堆叠技术下3D TLC闪存在改善功耗表现和提升存储密度与读写速度方面的优势。

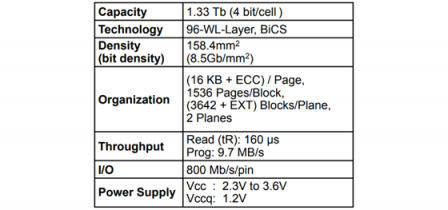

东芝的96层堆叠BiCS4闪存拥有TLC和QLC两种类型,后者的每个单元可以储存4比特数据,位密度8.5Gb/ mm²,相比TLC类型的512Gb 3D TLC提升40%以上。

东芝还披露,96层3D QLC闪存器件的芯片尺寸为158.4 mm²,利用改进后的源极 - 偏置 - 负检测方案,允许深负阈值电压,同时保持低电源电压。

针对QLC闪存的写入性能衰减问题,东芝还优化了两步写入(Program)方法,使典型Page页面编程写入时间减少18%,大幅提升了闪存的写入性能。

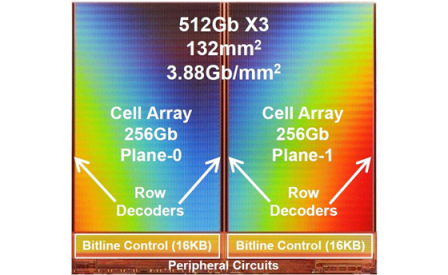

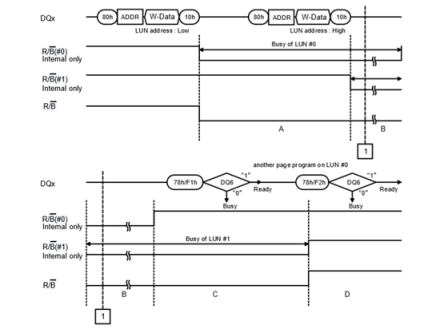

除了已经实现量产的96层堆叠BiCS4之外,东芝还讨论了未来的128层堆叠3D NAND设备(BiCS5)。TLC类型的BiCS5闪存能够实现66 mm²芯片尺寸和7.8Gb/ mm²的位密度。BiCS5还将采用包括四平面阵列、多芯片峰值功率管理和4KB页面读取模式在内的三种关键技术,提升闪存性能、精细化控制功耗。

下图是已经在BiCS3闪存当中应用的双平面闪存阵列,128层堆叠的下一代闪存中将使用更多的四平面阵列,从而提高每比特密度的闪存性能。

多平面闪存可通过Multi Plane交错,用分时传输/执行的方式执行交错读写、交错擦除,实现性能倍增。

东芝在1987年发明的NAND闪存正成为近年来存储技术飞速发展的驱动力,大容量、高性能的NAND闪存将加速家用电脑固态存储的普及。我们也将有机会用上更便宜、更好用的固态硬盘。

- 比亚迪整合五大子品牌为APP,打造一站式车主服务平台,体验升级中!

- 谷歌预警:警惕AI安全风险,公开防御蓝图

- 比亚迪起诉自媒体“智能EVO”:维权行动揭开名誉侵权黑幕

- 小米纸扎版SU7专利爆光,网友笑称清明节新爆款

- 微软暂停数据中心扩张计划:数据中心“退烧”,回归理性扩张

- 货拉拉力争2024年上市,营收增长19.39%达15.93亿美元,你准备好投资了吗?

- 巴西监管风暴下,苹果App Store应用追踪透明功能面临巨额罚款

- 中国快递协会严正声明:反对美取消“低价值包裹免税”政策,公平贸易不容欺诈

- 美股七巨头市值一夜蒸发逾万亿,金融风暴即将来临?

- 前华为智驾负责人苏菁:揭秘特斯拉自动驾驶真实水平,断代领先并非全然事实

免责声明:本网站内容主要来自原创、合作伙伴供稿和第三方自媒体作者投稿,凡在本网站出现的信息,均仅供参考。本网站将尽力确保所提供信息的准确性及可靠性,但不保证有关资料的准确性及可靠性,读者在使用前请进一步核实,并对任何自主决定的行为负责。本网站对有关资料所引致的错误、不确或遗漏,概不负任何法律责任。任何单位或个人认为本网站中的网页或链接内容可能涉嫌侵犯其知识产权或存在不实内容时,应及时向本网站提出书面权利通知或不实情况说明,并提供身份证明、权属证明及详细侵权或不实情况证明。本网站在收到上述法律文件后,将会依法尽快联系相关文章源头核实,沟通删除相关内容或断开相关链接。