随着图像像素和帧率的不断提高,传统的LVCOMS规格已经不能承载图像需要的带宽要求。在所有的替代方案中,7:1 LVDS 是一个相对性价比比较高的解决方案。其单个差分对可以达到500Mbps以上的传输速率,这是LVCOMS难以企及的。在液晶面板的图像接口中往往可以看到7:1 LVDS的身影。

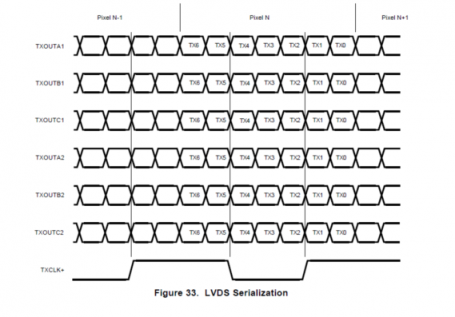

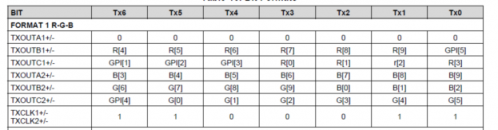

图像的RGB数据和控制数据经过编码后分散在几个通道中传输,并有一路7分频的同步时钟伴随。编码方式和时钟数据的相位关系是确定的,以TI的LM98620举例如下:

Figure 1 7:1 LVDS 编码格式

7:1 LVDS的发送设计相对容易,接收的时候看设计平台不同解决方案也略有不同。

Xilinx公司Spartan6系列的IO有数据同步功能,所以自带高速数据解串能力,设计相对容易。Lattice公司的XP2系列或者ECP3系列的IO虽然没有数据同步功能,但是利用IO DDR功能,加上芯片内置PLL相位调整相对灵活,网上也有成熟的参考设计。本文主要介绍使用国产安路FPGA实现低成本7:1 LVDS接收方案,并已经调试成功,稳定量产。

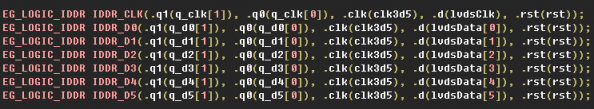

安路FPGA EG4系列和市场主流FPGA一样,基本结构也是基于SRAM的查找表。IO支持DDR和DDRx2的功能,LVDS实测速率可以达到500MHz;全系列内置4个PLL,每个最多支持输出5路时钟输出。这两个基本结构是实现7:1 LVDS的关键。

按照7:1 LVDS规范,如果TXCLK是70MHz,那么LVDS的数据实际速率已经达到了490Mbps。但是采用DDRIO以后,可以在EG4的IO接口上,用245MHz的时钟解串LVDS数据和TXCLK。这个245MHz的时钟就是7:1 LVDS时钟经过PLL 3.5倍频后得到的。

Figure 2 EG4 IDDR 实例化示例

首先要确定7:1 LVDS时钟的相位。TXCLK解串下来的数据可能是“1100011”,也可能是“0001111”,这个取决于245MHz时钟的相位而定。而且这个相位要现场调试一下,不同的硬件可能会略有差异。因为是内部信号,所以用示波器观察不是很方便。但是安路FPGA设计工具中自带嵌入式逻辑分析仪“ChipWatcher”,可以很方便的看到TXCLK解串后的数据。

根据7:1 LVDS的编码方式,一个TXCLK周期中包含了7个数据bit,而DDRIO每次解串下来是2个数据bit,所以实际解码的数据会分配在相邻的两个7:1 LVDS的周期中。比如,实际解码的TXCLK可能是“1100011”和“1000111”或者是“0001111”和“0011110”。

一旦获取稳定的TXCLK相位后,就可以根据上一页的表格定位出RGB数据的位置解出RGB数据。需要注意的是7:1 LVDS编码的RGB数据是10bit宽度,如果用户只需要8bit数据的话,要选取其中的高8位。

采用这个接收方案,已经在实际产品中稳定使用了。而且安路公司的FPGA开发软件TD安装简单,资源占用少,运行速度快,对绝大多数应用设计游刃有余。

安路科技根植中国,面向世界,积极参与国际竞争,努力成为中国可编程逻辑器件产业的主导企业和世界可编程逻辑器件解决方案的主要供应商。

- 戴尔破局未来:2025春季发布会揭示数智化转型新路径

- 2025上海车展前瞻:哈弗新能源,四驱赛道上的颠覆性选择

- 2025上海车展:科大讯飞引领智能汽车新革命,星火平台惊艳亮相

- 上海车展惊艳登场:中国双旗舰豪华车型揭秘,极氪9X全球首秀颠覆想象

- 日产汽车以创新新能源布局,为未来城市出行点亮新篇章

- 雅迪发布全球首款“碰一下”电动车:支付宝“碰一下”1秒解锁,还有骑行绿色能量

- 蚂蚁专属芯片研发:复旦微电下半年量产,打破智能硬件市场格局

- 支付宝新功能引爆年轻人市场,亿级用户破圈而来

- SK海力士逆袭成AI内存芯片新巨头?取代三星成新王?利润飙升背后的秘密

- 波音CEO回应定制飞机订单:有信心寻觅中国买家,破解航空市场新篇章

免责声明:本网站内容主要来自原创、合作伙伴供稿和第三方自媒体作者投稿,凡在本网站出现的信息,均仅供参考。本网站将尽力确保所提供信息的准确性及可靠性,但不保证有关资料的准确性及可靠性,读者在使用前请进一步核实,并对任何自主决定的行为负责。本网站对有关资料所引致的错误、不确或遗漏,概不负任何法律责任。任何单位或个人认为本网站中的网页或链接内容可能涉嫌侵犯其知识产权或存在不实内容时,应及时向本网站提出书面权利通知或不实情况说明,并提供身份证明、权属证明及详细侵权或不实情况证明。本网站在收到上述法律文件后,将会依法尽快联系相关文章源头核实,沟通删除相关内容或断开相关链接。