玻璃基板有助于克服有机材料的局限性,使未来数据中心和人工智能产品所需的设计规则得到数量级的改进。

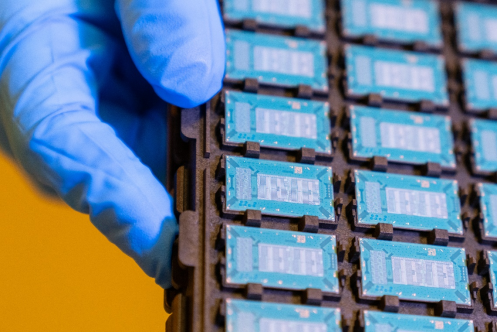

英特尔宣布在业内率先推出用于下一代先进封装的玻璃基板,计划在未来几年内向市场推出。这一突破性进展将使单个封装内的晶体管数量不断增加,继续推动摩尔定律,满足以数据为中心的应用的算力需求。

英特尔公司高级副总裁兼组装与测试技术开发总经理Babak Sabi表示;“经过十年的研究,英特尔已经领先业界实现了用于先进封装的玻璃基板。我们期待着提供先进技术,使我们的主要合作伙伴和代工客户在未来数十年内受益。“

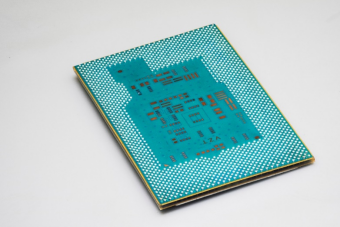

组装好的英特尔玻璃基板测试芯片的球栅阵列(ball grid array)侧

与目前采用的有机基板相比,玻璃具有独特的性能,如超低平面度(flatness)、更好的热稳定性和机械稳定性,从而能够大幅提高基板上的互连密度。这些优势将使芯片架构师能够为AI等数据密集型工作负载打造高密度、高性能的芯片封装。英特尔有望在未来几年内向市场提供完整的玻璃基板解决方案,从而使整个行业在2030年之后继续推进摩尔定律。

到2020年代末期,半导体行业在使用有机材料的硅封装中微缩晶体管的能力可能将达到极限,因为有机材料耗电量更大,而且存在收缩和翘曲等限制。晶体管微缩对半导体行业的进步和发展而言至关重要,因此,采用玻璃基板是迈向下一代半导体可行且必要的一步。

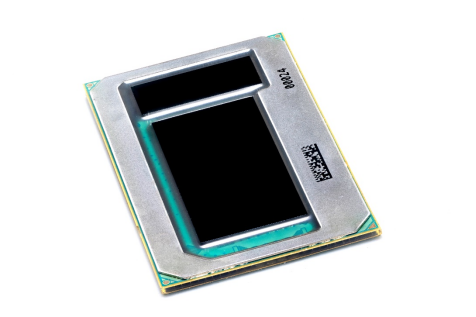

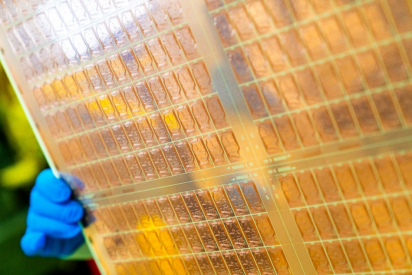

组装好的英特尔玻璃基板测试芯片的裸片装配(multi die assembly)侧

随着对更强大算力的需求不断增长,以及半导体行业进入在封装中集成多个芯粒的异构时代,封装基板在信号传输速度、供电、设计规则和稳定性方面的改进变得至关重要。与目前使用的有机基板相比,玻璃基板具有卓越的机械、物理和光学特性,可以在封装中连接更多晶体管,提供更高质量的微缩,并支持构建更大的芯片组(即“系统级封装”)。芯片架构师将有能力在一个封装中以更小的尺寸封装更多的芯粒模块,同时以更灵活、总体成本和功耗更低的方式实现性能和密度的提升。

玻璃基板测试单元

在用途方面,玻璃基板最先将被用于其更能发挥优势的地方,即需要更大尺寸封装和更快计算速度的应用和工作负载,包括数据中心、AI、图形计算等。

玻璃基板可耐受更高的温度,将变形(pattern distortion)减少50%,并具有极低的平面度,可改善光刻的聚焦深度(depth of focus),还达到了实现极紧密的层间互连叠加所需的尺寸稳定性。由于这些独特的性能,玻璃基板上的互连密度有望提升10倍。此外,玻璃机械性能的改进实现了非常高的超大尺寸封装良率。

玻璃基板对更高温度的耐受性,也让芯片架构师能够更灵活地设置电源传输和信号路由设计规则,因为它在更高温度下的工作流程中,提供了无缝集成光互连器件和将电感器和电容器嵌入玻璃的能力。因此,采用玻璃基板可以达成更好的功率传输解决方案,同时以更低的功耗实现所需的高速信号传输,有助于让整个行业更接近2030年在单个封装内集成1万亿个晶体管的目标。

测试用玻璃芯基板

此次技术突破,源于英特尔十余年来对玻璃基板作为有机基板替代品的可靠性的持续研究和评估。在实现用于下一代封装的技术创新方面,英特尔有着悠久的历史,在20世纪90年代引领了业界从陶瓷封装向有机封装的过渡,率先实现了无卤素和无铅封装,并发明了先进的嵌入式芯片封装技术和业界领先的主动式3D封装技术。因此,从设备、化学品和材料供应商到基板制造商,英特尔能够围绕这些技术建立起一个完整的生态系统。

英特尔在业界率先推出用于先进封装的玻璃基板,延续了近期PowerVia和RibbonFET等技术突破的良好势头,展现了英特尔对Intel 18A制程节点之后的下一个计算时代的预先关注和展望。英特尔正朝着 2030 年在单个封装上集成 1 万亿个晶体管的目标前进,而包括玻璃基板在内的先进封装技术的持续创新将有助于实现这一目标。

(免责声明:本网站内容主要来自原创、合作伙伴供稿和第三方自媒体作者投稿,凡在本网站出现的信息,均仅供参考。本网站将尽力确保所提供信息的准确性及可靠性,但不保证有关资料的准确性及可靠性,读者在使用前请进一步核实,并对任何自主决定的行为负责。本网站对有关资料所引致的错误、不确或遗漏,概不负任何法律责任。

任何单位或个人认为本网站中的网页或链接内容可能涉嫌侵犯其知识产权或存在不实内容时,应及时向本网站提出书面权利通知或不实情况说明,并提供身份证明、权属证明及详细侵权或不实情况证明。本网站在收到上述法律文件后,将会依法尽快联系相关文章源头核实,沟通删除相关内容或断开相关链接。 )