关于芯片行业,有一个灵魂拷问:什么是推动芯片发展的最根本动力?这个问题看起来是个送分题,答案绝大部分人都会脱口而出:摩尔定律。

每隔18-24个月,芯片上的晶体管数量就会增加一倍。但是,“晶体管数量本身并没有太多意义,有意义的是如何把这些多出来的晶体管用起来”,芯片大神Jim Keller曾经这样说过。所以晶体管数量的变化,其实反映着功耗、性能、面积、成本的变化。明确了这一点,就可以衍生出很多相关的推论,比如晶体管数量如果不变,芯片面积就会缩小一半、或者功耗缩减一半;面积如果不变,性能就会提升一倍,价格会降低一半,等等等等。

但是很多人也都在考虑另外一个问题:摩尔定律究竟描述的是表象,还是本质?上世纪六七十年代,戈登摩尔提出这个“定律”的时候,其实是在总结和描述芯片发展的规律。他的本意,并不是用这个规律来指导整个产业的发展。与其说摩尔定律像个指挥千军万马的将军,它更像是一面旗帜,代表了人们对于芯片产业不断发展的信心。

那么,究竟什么是推动芯片发展的根本动力?

从本质上来看,是需求。供需关系是经济学里最基础的概念,芯片行业几乎所有大大小小的创新与进步,其实都是基于需求的驱动。拿FPGA来举例,我们一直说它是延续摩尔定律最好的例子。并不是因为FPGA在盲目增加晶体管数量,而是它根据不同的需求,很好的把这些额外的晶体管利用起来了。

FPGA从最早期的逻辑验证芯片,发展到网络通信设备中的重要组成部分,再发展到今天数据中心里的核心单元,这个过程就是在不断发现需求、满足需求、创造需求的循环。

2021年12月7号-10号,英特尔举行了2021英特尔 FPGA技术大会,并且分享了很多FPGA技术与产品的最新进展。从这次的活动里,我们就能非常清楚的看到,需求如何改变了FPGA芯片发展的轨迹。我们接下来就一个一个的说。

1、FPGA的新作用

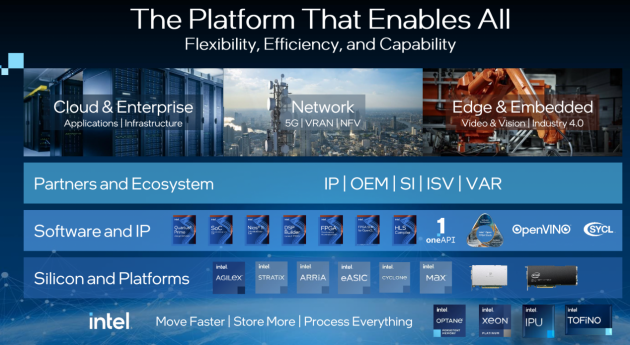

提到FPGA的用途,很多人还停留在原型验证和硬件仿真上,这未免有些一叶障目了。拨开眼前这片树叶,你会发现FPGA已经用在太多地方了。用英特尔公司副总裁,FPGA 和电源产品事业部、数据中心和人工智能事业部、可编程解决方案事业部总经理Patrick Dorsey的话说,FPGA可以用来加速云、端、及其中间的全部应用。

这就是FPGA的现状,远远不止原型验证,也远不止网络通信,而是作为高吞吐量、高能耗比的硬件加速单元,去加速你能想到的所有应用。当然,FPGA只是整个链条中的一个环节。如果从更高的高度往下看,英特尔的另外一句很有名的口号,就很好的概括了所有需求:“移动更快、存储更多、处理一切。Move fast, Store more, Process everything.”

为了满足这样的需求,必然不能通过一种架构、一种产品、一种方案来实现。我们需要芯片、需要板卡、需要IP、需要开发软件,也需要健康的生态,这些都是FPGA不断进化的方向。

2、Agilex FPGA的新提升

如果穿越回N年前(N大于等于5),给当时的工程师说FPGA现在长这样,估计绝大部分人都会惊掉下巴。特别是Agilex FPGA,更是和传统的FPGA架构有着巨大差别。

Agilex这个名称源于Agile(敏捷)和Flexible(灵活)的合二为一。相比于其他指标,比如性能、功耗、成本,Agile + Fexible这两点才是业界对现代FPGA的最迫切需求。

也就是说,人们不仅需要一个高吞吐量、高带宽、高逻辑单元的性能猛兽,更需要一个灵活性强、适用性广,开发简单高效的器件。只有这样,才能更好的履行“硬件加速器”的职责,才能符合前面说的大方向:移动更快、存储更多、处理一切。

从架构和技术的角度详细分析Agilex的改进与提升,总结起来主要有6个主要方面:

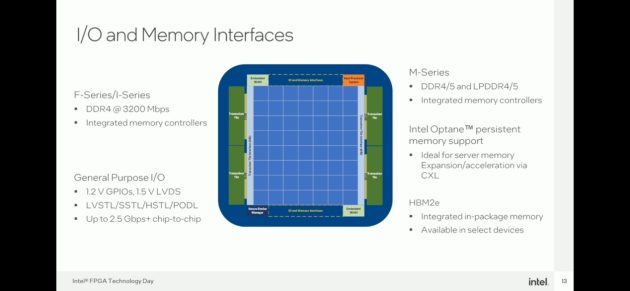

1、全新的芯片布局

2、新一代HyperFlex寄存器架构

3、多样的时序优化方法

4、英特尔10纳米SuperFin工艺

5、系统级3D芯片

6、更灵活的DSP和布线微架构

举例来说,Agilex的芯片布局进行了大修,把通用I/O、存储器I/O、SRAM等等单元都移到了芯片的上下两端。原本这些单元都在芯片中间按列分布,这会把芯片分割成很多个小的设计区域,容易造成布线拥堵和延时。Agilex的新型芯片布局,就从根本上规避了这些问题,从而加速设计的时序收敛。

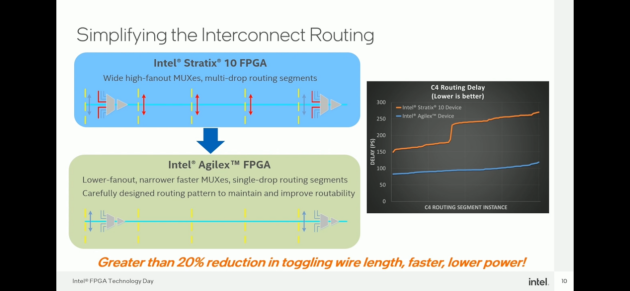

另外一个例子就是Agilex的HyperFlex寄存器架构。这种结构从Stratix10 FPGA里首次获得采用,到Agilex已经发展到了第二代。事实上,HyperFlex的想法是非常理想的,也就是在FPGA的布线资源上插入很多小寄存器,可以将时序路径分割成更小的部分,从而极大提升系统的工作频率。

但是这种方案实施起来,就遇到很多问题。比如HyperFlex寄存器本身会引入额外的延时,每个小寄存器的扇出数量,也会对系统性能造成负面影响。另外加入了这么多额外的单元,又对设计软件的自动化算法提出了挑战。其实,这些问题很多都在Stratix10里真实存在。

也就是说,HyperFlex的思路没错,但是实施方式出现了问题。所以,Agilex改进了Stratix10里第一代HyperFlex的设计缺陷,从原本更宽的多扇出设计,改成了现在更窄的少扇出设计,同时简化了HyperFlex寄存器本身的设计,减少了旁路延时。FPGA的基本组成单元ALM,也进行了重新设计,单独增加了额外的输出端口,可以直连HyperFlex寄存器。这些优化设计,都让Agilex的性能取得了大幅提升。根据英特尔的数据,仅是HyperFlex相关的改进,就将延时降低了超过20%。

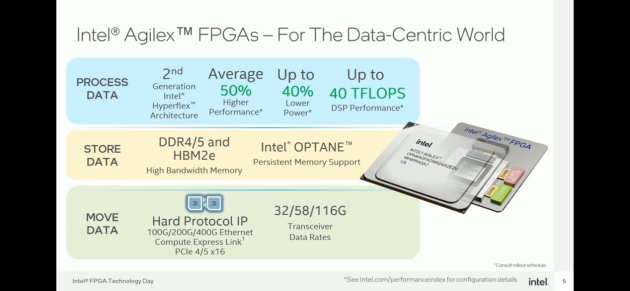

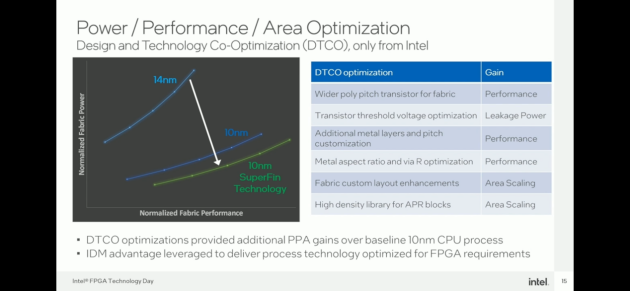

当然还值得一提的是Agilex的制造工艺。它采用了英特尔的10纳米SuperFin工艺。它比英特尔的基础10纳米工艺取得了进一步提升。相比14纳米的Stratix10,Agilex更是取得了平均50%的性能提升、以及高达40%的功耗降低。

和赛灵思的7纳米旗舰产品Versal相比,Agilex也可以取得1.42倍的性能提升,以及超过30瓦的功耗降低。

那么,什么是驱动这些提升的根本动力?就是数据中心对算力的需求、是边缘计算对延时的需求、是各种数据和应用对存储容量、数据传输速度的需求。

归根到底,都是各种需求。于是,FPGA上集成了更多晶体管、更多IP、更强大的收发器,原本的架构不够用,就设计新的架构,更好的利用这些多出来的晶体管。

所有这些,又会进一步延续摩尔定律的发展。

3、如何编程FPGA

还想简单说说FPGA的编程方法。基于RTL的设计仍然是开发FPGA的主流手段,但是更多高层次开发方法也在不断发展。

Quartus软件变的越来越智能,它不再把所有芯片一视同仁,也不再把芯片上的所有位置和部分一视同仁,而是根据大量的测试数据,分区域进行功耗和时序的优化。把更长的时序路径,放在更快的区域,把不那么长的路径,放在稍微慢一点的位置,从而实现整体的优化提升。

这些技术进步,说起来就寥寥几句,但实现起来又何其复杂。只有能用起来的芯片,才有价值。EDA软件一直是FPGA厂商“皇冠上的明珠”,因为它的使命就是让芯片更好用。

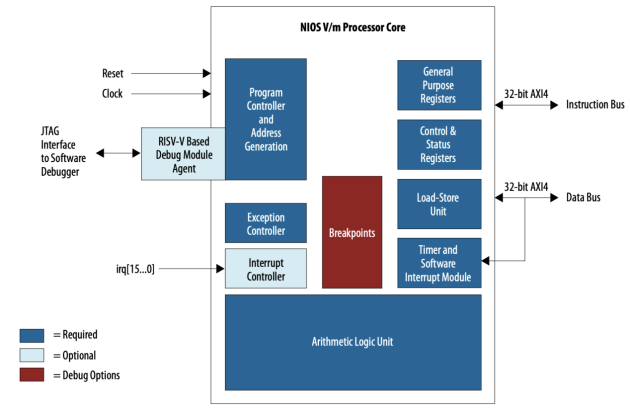

为了提升可用性,英特尔又把RISC-V放到了FPGA里,提出了名叫Nios V的软核处理器。它有5级流水线和AXI4接口,比之前的NiosII处理器性能提升了5倍。但更重要的是,用户可以直接基于RISC-V生态进行软件开发,而不需要额外学习Nios了,这才是Nios V的最大意义。

结语

现在或许是从事FPGA行业最好的时代,不管是FPGA芯片本身,还是FPGA的应用,都有太多新的机会。我们完全不必纠结摩尔定律是否已经临近终结,只要需求还在,技术的进步就不会停息。

英特尔FPGA线上技术大会(12月7~10)正在进行,欢迎前往英特尔FPGA技术大会官网注册报名。

(免责声明:本网站内容主要来自原创、合作伙伴供稿和第三方自媒体作者投稿,凡在本网站出现的信息,均仅供参考。本网站将尽力确保所提供信息的准确性及可靠性,但不保证有关资料的准确性及可靠性,读者在使用前请进一步核实,并对任何自主决定的行为负责。本网站对有关资料所引致的错误、不确或遗漏,概不负任何法律责任。

任何单位或个人认为本网站中的网页或链接内容可能涉嫌侵犯其知识产权或存在不实内容时,应及时向本网站提出书面权利通知或不实情况说明,并提供身份证明、权属证明及详细侵权或不实情况证明。本网站在收到上述法律文件后,将会依法尽快联系相关文章源头核实,沟通删除相关内容或断开相关链接。 )